# The Simulation and Visualization of Parallel BMF Code

Paul Martinaitis

Department of Computer Science University of Adelaide

## SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE HONOURS DEGREE IN COMPUTER SCIENCE

November 1998

Rev 1.1

## ABSTRACT

This project concerned the design and implementation of a tool which would enable the simulation and subsequent visualisation of parallel BMF code on a "virtual" architecture. This thesis will begin by giving a brief review of the wider context in which the project was conducted. The Bird-Meertens Formalism (or BMF) will be introduced from a programmers point of view and indications of the way in which BMF code may be parallelized through an automatic transformation process will be discussed. The design and construction of the simulator itself will then follow - along with the visualization methodology used. Results of the simulator will be presented as well as some extension made to the network module which facilitate the modeling of congestion.

# ACKNOWLEDGEMENTS

I would firstly like to wholeheartedly thank my supervisor Brad Alexander for all his help and patience during the year and for introducing me to such an interesting area of study. I would like to also thank my parents who have always supported me through out my studies and were there to help when needed. My friends, especially Paul and Peter also deserve special mention for their support and good times.

# TABLE OF CONTENTS

| ABSTRACTI |        |                                         |    |  |  |

|-----------|--------|-----------------------------------------|----|--|--|

| A         | CKNOW  | VLEDGEMENTS                             | II |  |  |

| T         | ABLE O | DF FIGURES V                            | 'I |  |  |

| 1.        | INTI   | RODUCTION                               | 1  |  |  |

|           | 1.1    | ABSTRACT MODELS OF PARALLEL COMPUTATION | 1  |  |  |

|           | 1.2    | THE BIRD-MEERTENS FORMALISM             | 2  |  |  |

|           | 1.2.1  | Completness                             | 3  |  |  |

|           | 1.3    | AUTOMATED OPTIMIZATION                  | 3  |  |  |

|           | 1.4    | ROLE OF THE PROJECT                     | 4  |  |  |

|           | 1.5    | PROJECT OVERVIEW                        | 5  |  |  |

|           | 1.6    | OVERVIEW OF THIS THESIS                 | 5  |  |  |

| 2.        | THE    | BIRD-MEERTENS FORMALISM                 | 7  |  |  |

|           | 2.1    | INTRODUCTION                            | 7  |  |  |

|           | 2.2    | Syntax                                  | 7  |  |  |

|           | 2.3    | BMF PROGRAMS                            | 8  |  |  |

|           | 2.4    | DATA TYPES                              | 9  |  |  |

|           | 2.4.1  | Lists                                   | 9  |  |  |

|           | 2.4.2  | Tuples                                  | 9  |  |  |

|           | 2.5    | PROGRAM CONSTRUCTORS                    | 10 |  |  |

|           | 2.5.1  | Composition                             | 10 |  |  |

|           | 2.5.2  | All-Applied-To                          | 10 |  |  |

|           | 2.6    | CONSTANTS                               | 11 |  |  |

|           | 2.7    | OPERATORS                               | 11 |  |  |

|           | 2.7.1  | Binary 'Operators'                      | 11 |  |  |

|           | 2.7.2  | Unary Operators                         | 13 |  |  |

|           | 2.7.3  | Aggregate Operators over Lists          | 13 |  |  |

|           | 2.8    | PARALLEL BMF CODE                       | 15 |  |  |

|           | 2.9    | PARALLEL OPERATORS                      | 17 |  |  |

|           | 2.9.1  | P_Split                                 | 17 |  |  |

|           | 2.9.2  | <i>P_Map</i>                            | 18 |  |  |

|           | 2.9.3  | P_Reduce                                | 18 |  |  |

| 2.9    | .4 P_Scan                                |  |

|--------|------------------------------------------|--|

| 2.9    | .5 P_Zip                                 |  |

| 2.9    | .6 P_Distl                               |  |

| 2.9    | .7 P_Project                             |  |

| 2.10   | PARALLELISATION OF SERIAL BMF CODE       |  |

| 3. VIS | SUALISATION METHODOLOGY                  |  |

| 3.1    | INTRODUCTION                             |  |

| 3.2    | PICL                                     |  |

| 3.2    | .1 PICL Tracefile Format                 |  |

| 3.2    | .2 Basic Trace Record Structure          |  |

| 3.2    | .3 Events and Event Specific DataFields: |  |

| 3.2    | .4 Example PICL Trace Records            |  |

| 3.3    | THE TRACE MODULE                         |  |

| 3.4    | Paragraph                                |  |

| 3.4    | .1 Events                                |  |

| 3.5    | PARAGRAPH EXAMPLES                       |  |

| 4. TH  | E PARALLEL BMF SIMULATOR                 |  |

| 4.1    | Overview                                 |  |

| 4.2    | IMPLEMENTATION OF DATATYPES              |  |

| 4.2    | .1 Lists and Tuples                      |  |

| 4.2    | .2 Values                                |  |

| 4.3    | FRONT END                                |  |

| 4.3    | .1 Scanner                               |  |

| 4.3    | .2 Parser                                |  |

| 4.4    | INTERNAL REPRESENTATION OF BMF PROGRAMS  |  |

| 4.4    | .1 Higher Order Constructs               |  |

| 4.4    | .2 'Operators' under B_OP                |  |

| 4.4    | .3 Miscellaneous Constructs              |  |

| 4.5    | EVALUATOR                                |  |

| 4.6    | Modelling of Parallel Execution          |  |

| 4.6    | .1 Tags                                  |  |

| 4.6    | .2 Machine Module                        |  |

| 4.6    | .3 Inter-Process Communications          |  |

| 4.7    | INTERCONNECTION NETWORK MODELLING        |  |

| 4.7    | .1 Normal Send                           |  |

| 4.7    | .2 Delayed Send                          |  |

| 4.7    | .3 Cost Modelling                        |  |

| 5. RE  | SULTS FOR FUNDAMENTAL CONSTRUCTS         |  |

|    | 5.1   | OVERVIEW                                       | . 50 |

|----|-------|------------------------------------------------|------|

|    | 5.2   | COMMENTS ON VISUALISATION DISPLAYS             | . 50 |

|    | 5.3   | P_Split                                        | . 50 |

|    | 5.3.1 | B_Split                                        | . 51 |

|    | 5.3.2 | Split_Parallel                                 | . 51 |

|    | 5.3.3 | Simulation Results for P_Split                 | . 54 |

|    | 5.3.4 | Nested Splits                                  | . 56 |

|    | 5.4   | P_DISTL                                        | . 58 |

|    | 5.4.1 | Results for P_Distl                            | . 58 |

|    | 5.5   | Р_Мар                                          | . 62 |

|    | 5.6   | P_REDUCE                                       | . 62 |

|    | 5.7   | P_Z <sub>P</sub>                               | . 70 |

|    | 5.8   | P_SCAN                                         | . 72 |

|    | 5.9   | P_PROJECT                                      | . 78 |

| 6. | EXT   | ENSIONS TO THE NETWORK MODEL                   | . 82 |

|    | 6.1   | OVERVIEW                                       | . 82 |

|    | 6.2   | MODELLING OF NETWORK TOPOLOGY                  | . 82 |

|    | 6.2.1 | Representation of Network Topology             | . 82 |

|    | 6.2.2 | Route Matrix                                   | . 83 |

|    | 6.3   | MODELLING OF CONGESTION                        | . 84 |

|    | 6.3.1 | Link Contention                                | . 84 |

|    | 6.3.2 | Network Package Extensions to Model Congestion | . 85 |

|    | 6.4   | EXAMPLES USING THE EXTENDED NETWORK MODEL.     | . 86 |

| 7. | CON   | ICLUSIONS                                      | . 92 |

| 8. | ΑΡΡ   | ENDIX A                                        | .93  |

|    | 8.1   | BNF DESCRIPTION OF BMF SOURCE CODE             |      |

|    |       |                                                |      |

| 9. | BIBI  | LIOGRAPHY                                      | . 95 |

# TABLE OF FIGURES

| Figure 1-1: Logical Overview of the Simulator                | 5  |

|--------------------------------------------------------------|----|

| Figure 3-1: Logical Structure of Simulator                   | 27 |

| Figure 3-2: Processor State Transition Diagram               | 30 |

| Figure 3-3: Example Gantt Chart                              | 32 |

| Figure 3-4: Example Space-Time Diagram                       | 33 |

| Figure 4-1: Logical Structure of the Simulator               | 34 |

| Figure 4-2: Ada List Node Definition                         | 35 |

| Figure 4-3: Ada Value Specification                          | 36 |

| Figure 4-4: Ada Specification of Parse Tree Node             | 38 |

| Figure 4-5: Communications Timeline                          | 46 |

| Figure 4-6: Space-Time Diagram of Project using Normal Send  | 47 |

| Figure 4-7: Space-Time Diagram of Project using delayed send | 49 |

| Figure 5-1: Data Distribution for P_Split Split Operation    | 52 |

| Figure 5-2: Variables used in Split_Parallel                 | 53 |

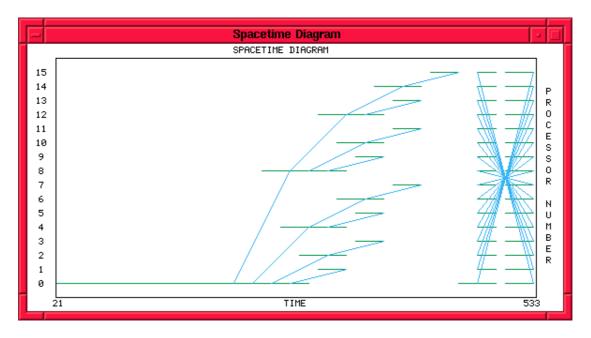

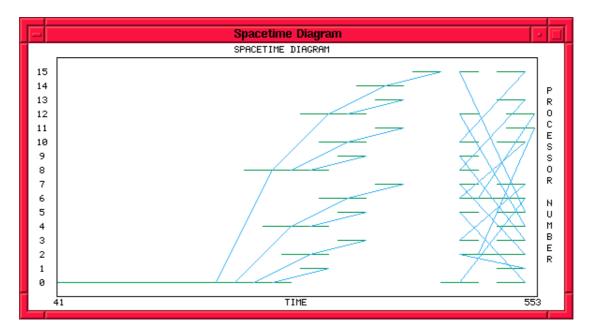

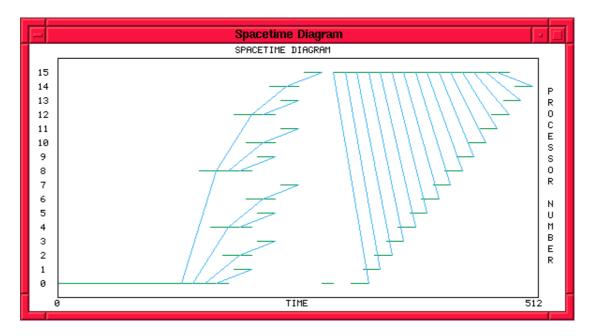

| Figure 5-3: Space-Time Diagram of Split(8)                   | 54 |

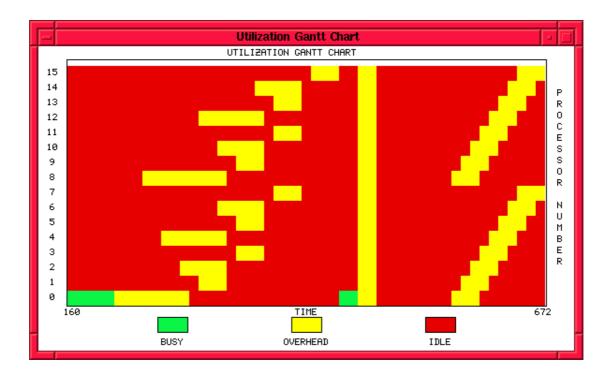

| Figure 5-4: Gantt Chart for Split(8)                         | 55 |

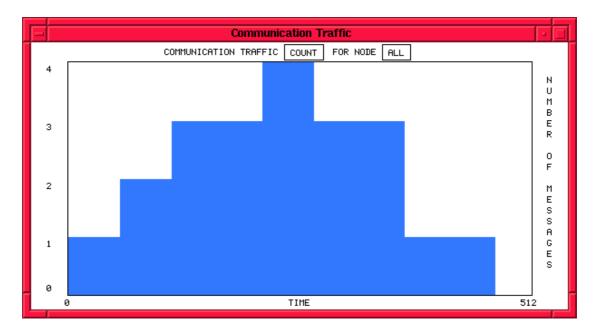

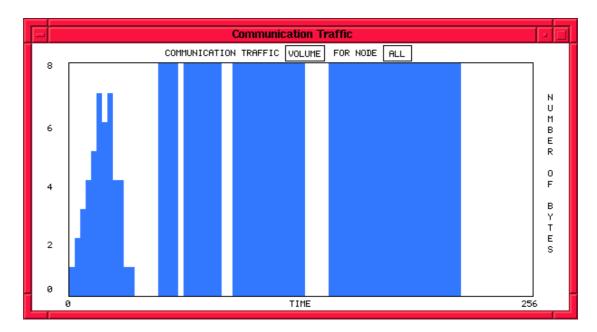

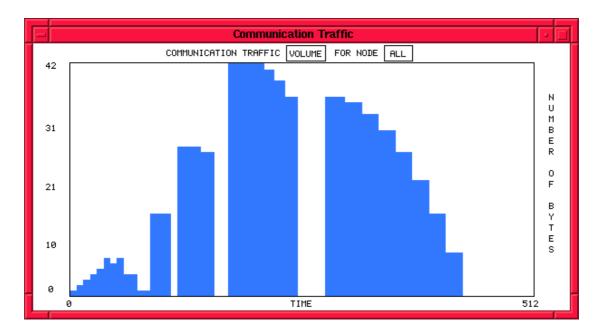

| Figure 5-5: Traffic Volume for Split(8)                      | 56 |

| Figure 5-6: Space-Time Diagram for Nested Split              | 57 |

| Figure 5-7: Space-Time Diagram of P_Distl                    | 59 |

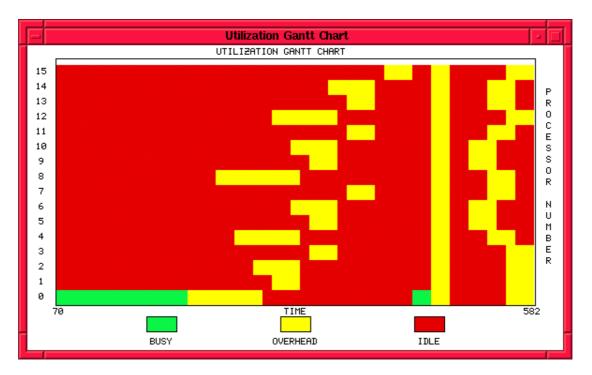

| Figure 5-8: Gantt chart of P_Distl operation                 | 59 |

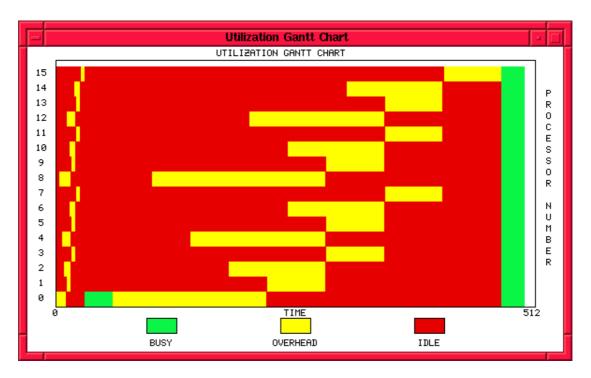

| Figure 5-9: Gantt Chart of Large P_Distl Operation           | 60 |

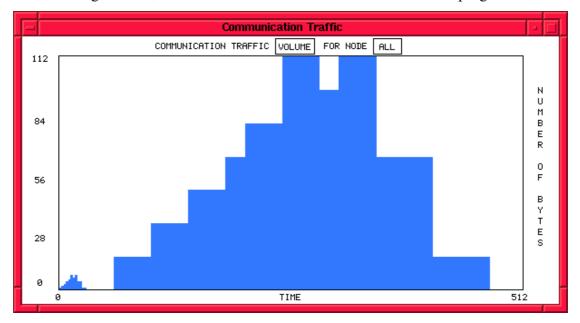

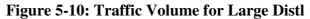

| Figure 5-10: Traffic Volume for Large Distl                  | 61 |

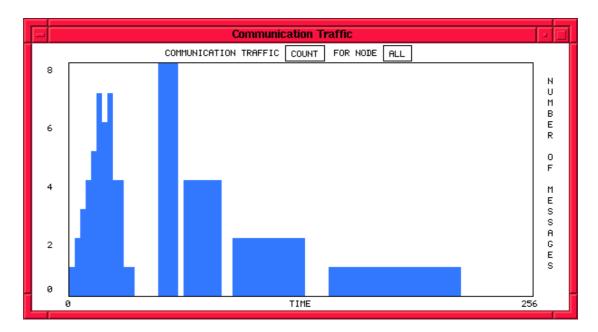

| Figure 5-11: Traffic Count for Large Distl                   | 61 |

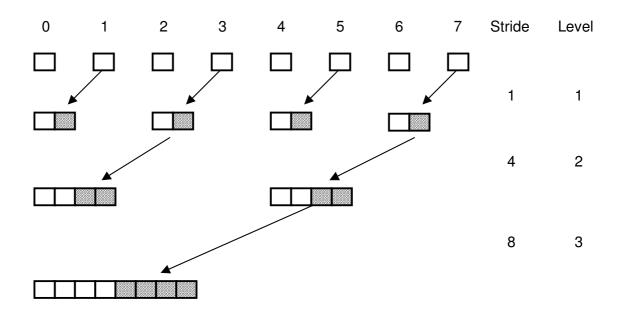

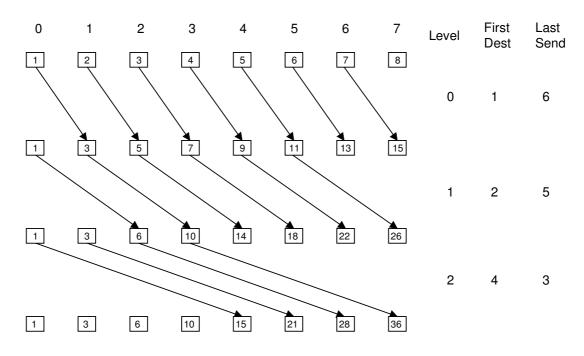

| Figure 5-12: Schmatic representation of P_Reduce             | 63 |

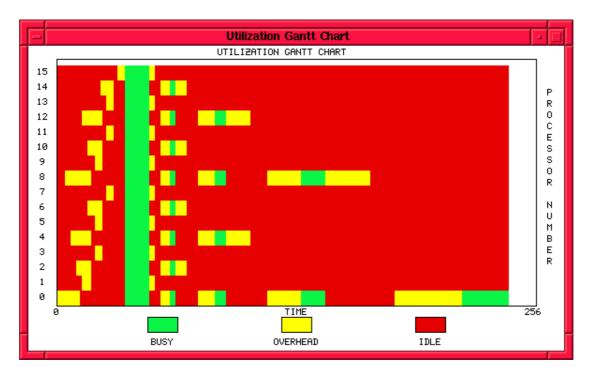

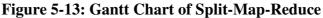

| Figure 5-13: Gantt Chart of Split-Map-Reduce                 | 64 |

| Figure 5-14: Space-Time Diagram of Split-Map-Reduce          | 65 |

| Figure 5-15: Traffic Volume for Split-Map-Reduce             | 66 |

| Figure 5-16: Traffic Count for Split-Map-Reduce              | 67 |

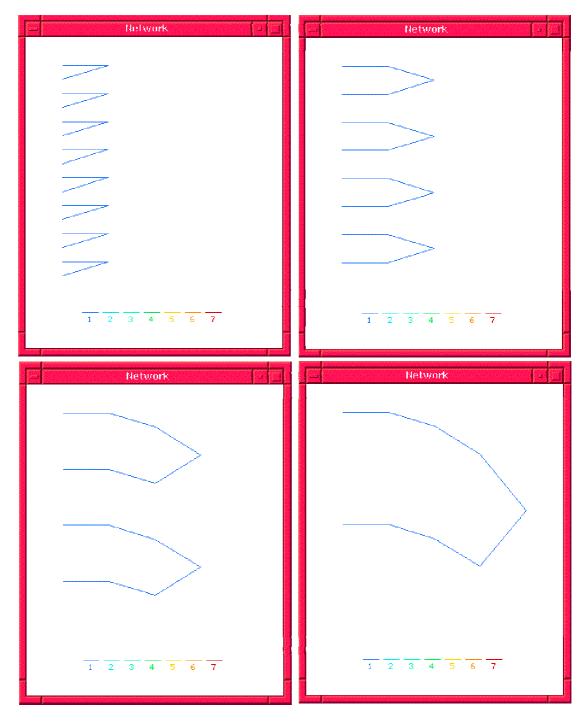

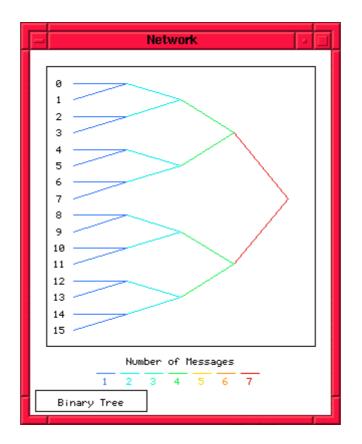

| Figure 5-17: Binary Tree Network Animation for Reduce        | 68 |

| Figure 5-18: 4x4 Mesh Network Animation for Reduce           | 69 |

| Figure 5-19: Space-Time diagram of Parallel Zip              | 71 |

| Figure 5-20: Gantt chart of Parallel Zip                                    | 71 |

|-----------------------------------------------------------------------------|----|

| Figure 5-21: Schematic of Parallel Scan                                     | 72 |

| Figure 5-22: Space-Time Diagram for Parallel Scan with Plus                 | 74 |

| Figure 5-23: Gantt Chart of Scan with Plus                                  | 74 |

| Figure 5-24: Traffic Volume for Scan with Plus                              | 75 |

| Figure 5-25: Space-Time Diagram for Scan with Concatenate                   | 76 |

| Figure 5-26: Gantt Chart of Scan with Concatenate                           | 77 |

| Figure 5-27: Traffic Volume for Parallel Scan with Concatenate              | 77 |

| Figure 5-28: Space-Time Diagram for List Reversal                           | 79 |

| Figure 5-29: Space-Time Diagram for Random Permutation of List              | 80 |

| Figure 5-30: Space-Time Diagram of 'Broadcast' with Project                 | 80 |

| Figure 6-1: Binary Tree Network Schematic                                   | 83 |

| Figure 6-2: Occupancy Matrix Time-Line                                      | 84 |

| Figure 6-3: Insertion of New Time Interval into Matrix Time-Line            | 85 |

| Figure 6-4: Gantt Chart of Scan using Basic Network Model                   | 87 |

| Figure 6-5: Gantt Chart of Scan on Binary Tree Network                      | 87 |

| Figure 6-6: Network Diagram For Last Stage of Scan on a Binary Tree Network | 88 |

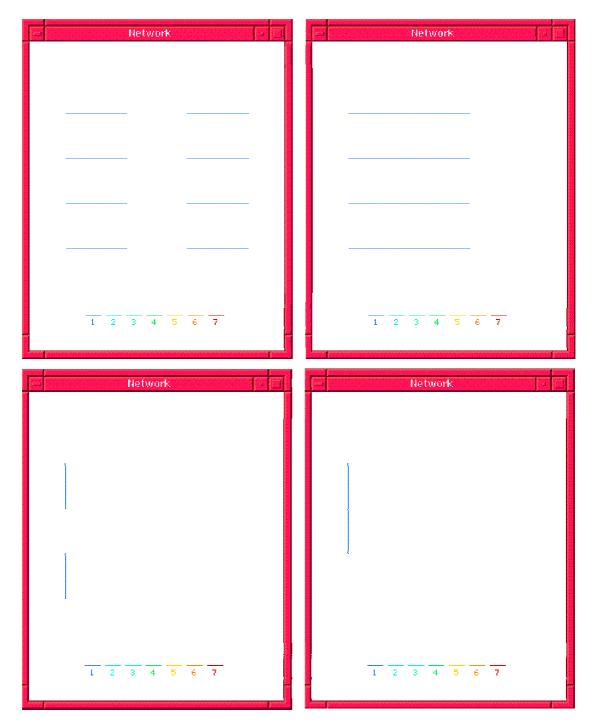

| Figure 6-7: Space-Time Diagram for Project on Binary Tree Network           | 89 |

| Figure 6-8: Space-Time Diagram of Project on 4x4 Mesh Network               | 89 |

| Figure 6-9: Gantt Chart for Project on 4x4 Mesh Network                     | 90 |

## 1. Introduction

Over the years, few areas of computer science research have shown as much promise in terms of increased performance and expansion in the domain of solvable problems than that of highly parallel computation. To date, a large number of innovative parallel architectures have been proposed with many of them having actually been constructed. Yet, in spite of this progress, few of these architectures are widely used in industry and the wider research community. A major reason for the under-utilization of these architectures lies not with the hardware as such, but rather with the high costs involved with the development and maintenance of the associated software. The difficulties with the software arise largely because in many cases, the programming models used on such machines are too architecturally specific; this increases the semantic gap between the high-level description of a problem and its implementation. Such a disparity not only increases the burden on the programmer but, more significantly, also makes the re-targeting of a program to different hardware platforms quite difficult. It is this latter point that is most troublesome because, for any given problem domain, the current best performing architecture at any given time can change quite rapidly and application software must be modified to keep up with such changes; it is this necessity to rewrite software for each new architecture that makes maintenance of parallel software so expensive. Clearly then, to facilitate the easier development of software that is more amenable to transfer between a variety of different architectures, less architecture specific models of computation are required.

## 1.1 Abstract Models of Parallel Computation

Skillicorn [17, 18] gives several key characteristics that a suitable parallel computational model should have if it is to be of greatest use. Firstly, the model needs to be sufficiently architecturally independent that it can be mapped to any of the commonly available parallel architectures. Secondly, the model should be Congruent; meaning that the complexity of a program at the model level should map in a 'linear' way to its implementation on the target machine. Finally, the model should be cognitively simple so that the programmer is insulated from the burden of dealing

with low level aspects of the architecture such as synchronization, communications, topology etc.: such abstraction greatly increases productivity and code readability at low levels of parallelism and becomes a necessity with massive parallelism which would otherwise become impossible to reason about effectively.

## 1.2 The Bird-Meertens Formalism

Quite a number of models for parallel computation have been proposed, each necessarily being a compromise between the above-mentioned factors as well as a number of others such as expressiveness and ease of implementation[17]. The so-called data-parallel models<sup>1</sup> are considered to be among the simplest in terms understandability from the programmer's point of view as well as generally satisfying the criteria discussed above. The Bird-Meertens formalism[1, 2, 3, 8, 9, 15, 16, 17, 18, 19] or BMF is one such model that has a firm theoretical basis in categorical data types and their attendant operations.

This foundation gives it a number of additional useful properties including:

- Predictable computational patterns which assists both in the efficient implementation of BMF constructs and also in the reasoning about code behavior.

- Low minimum requirements on the underlying architecture resulting in lower implementation complexity and greater portability.

- Predominantly local communication patterns which serve to greatly increase the efficiency of implemented code.

- A completeness property which guarantees that any two equivalent computational forms (programs) may be transformed from one into another by the application of a finite number of algebraic steps.

<sup>&</sup>lt;sup>1</sup> A data-parallel model is one which achieves parallelism through the application of the same instructions, simultaneously, over a set of data[5].

#### 1.2.1 Completness

It is the completeness property which is perhaps the most significant feature of BMF as a programming model. What this property allows one to do is to take an initial program that is close to its specification and transform it into one that is computationally equivalent, but more efficient: because this process is a mathematical one, correctness of the process is assured. Furthermore, completeness guarantees that if an optimally efficient form of a program exists, then it can be reached in a finite number of steps: this combined with the fact that any step is reversible, means that the optimization of a program can be reduced to the traversal of a finite, albeit potentially very large, search space. Unfortunately it turns out that for any non-trivial program, the search space becomes intractably large thus precluding the use of blind search strategies.

#### 1.3 Automated Optimization

As discussed above, expressing a program in BMF provides a sound basis for transforming a program from one form to another without affecting correctness. Such transformations are normally carried out with the aim of optimizing program performance. Performance enhancement is achieved by a combination of optimization of sequential code, cf. the data movement optimizer in the Adl project[3,4], and parallelization, or partitioning, of the code by exploiting the natural parallelism present in the BMF operators. At the present time, the large search space means that optimizations are performed by hand, particularly in the case of parallelization; current automatic optimization systems typically make use of a limited set of generally applicable transformations, however, it is hoped that in the future more sophisticated heuristic search techniques can be developed which will narrow the search space and make use of automatic optimization and parallelization more attractive.

Although the BMF model is reasonably architecturally independent, it must ultimately be implemented on a variety of real architectures, each having different physical characteristics. Such architectural differences will affect the degree to which particular program features and transformations impact upon program performance. For example, a system using a cross-bar network would generally experience substantially less congestion than, say, a binary tree. As a result when developing the heuristics, it is necessary to use knowledge of relationships between architectural parameters and transformations to steer the search in the 'direction' that will have the greatest probability of yielding the most effective optimizations on that particular architecture. At the present time, the required architecture specific information, available to guide us, is minimal; it is this gap in knowledge that the project attempts to go some way towards addressing.

## 1.4 Role of the Project

This project aims to the design and implement a tool which simulates the execution of parallel BMF code on a virtual architecture and allow subsequent visualisation, of an execution trace, using the Paragraph package. It is intended that such a tool will be used as an experimental platform to facilitate the exploration of the relationships between various architectural parameters and program transformations without the expense of actually of porting a full BMF system to each hardware platform. This investigation is carried out with the aim of increasing the knowledge base of architecture specific information which ultimately assists in the development more sophisticated heuristics leading to a greater use of automated optimization.

### 1.5 Project Overview

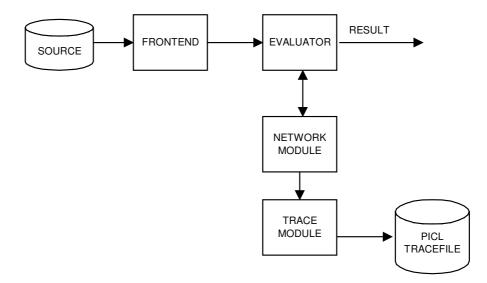

#### Figure 1-1: Logical Overview of the Simulator

Figure 1-1 shows the logical structure of and relationships between the major components of the simulator constructed in this project. A brief conceptual view of the way in which the simulator works is as follows: the Parallel BMF code is read in from an ASCII file, scanned and parsed by the Frontend and then sent to the Evaluator. The Evaluator simulates the parallel execution of the code producing the result (output) of the program as well as interacting with the Network Module to generate a PICL tracefile. Finally, Paragraph is used to visualize the execution of the program using the tracefile.

### 1.6 Overview of this Thesis

Chapter 2 introduces BMF 'source' code from an operational viewpoint, discussing the constructs available and how BMF programs may be written. Parallel BMF and the parallelization process will also be discussed. The details of the visualization methodology used by the simulator will be covered in chapter 3. In particular, the PICL tracefile format which may in some sense be regarded as the target code produced by the tool will be introduced and its relationship to the visualisation package Paragraph discussed. Chapter 4 will then look at the details of the simulator itself including how the parallelism and the interconnection network of the virtual architecture are simulated. The fundamental parallel operators of BMF will be examined in chapter 5 with visualisation results produced by the simulator being used to illustrate the nature of the operators.

Towards the end of the project, some extensions were made to the interconnection network model of the virtual architecture to take account of various different network topologies and congestion. Chapter 6 will outline how the more sophisticated modeling was carried out before highlighting the difference that the more realistic model makes to the visualisation results. The effects that different architectures can have on program performance will then be examined by way of some examples.

Chapter 7 will summarize the results and discuss the conclusions reached before outlining some future research directions that have arisen as a result of the work undertaken in this project.

## 2. The Bird-Meertens Formalism

## 2.1 Introduction

The Bird-Meertens Formalism (or BMF[8, 9]) is a theoretical framework, based on categorical data types, which enables the development of a well defined calculus to facilitate program transformation; such a theory has been built for a number of data types including: cons lists, concatenate lists, trees, arrays and bags[8, 14, 19, 20]. The BMF theory of concatenate lists, used exclusively in this project, is particularly well developed and its operations have potentially parallel implementations; this would not be possible with inherently sequential data types such as cons-lists. There are a number of different levels at which BMF can be discussed ranging from its theoretical underpinnings in Category theory through to its use as a practical programming language. In this chapter, the latter approach will be taken by providing an overview of the BMF source code used by the simulator whilst also introducing the notion of parallel BMF code.

## 2.2 Syntax

BMF, being a largely theoretical language, has no universally defined standard notation in which programs may be expressed; virtually any, practical, internally consistent notational system may be used. The syntactical form chosen to express the BMF source code for this project is essentially the same as that produced by the Adl compiler thus allowing automatically generated code to be fed straight into the simulator. Appendix A contains the definition of the syntax for the source code expressed in Extended Backus Naur Form (EBNF).

#### 2.3 BMF Programs

A BMF program consists of a BMF expression juxtaposed with a single argument: in keeping with the functional nature of BMF, the argument encapsulates the entire input state of the program. The BMF expression in the program is either a single function or, more usually, a composition of functions. For example

#### B\_Id 1

is a very simple program which applies the identity function to the argument literal 1. A more complex program, involving a number of operations would need to use the composition operator, B\_Comp:

B\_Comp (\$Increment) (B\_Id) 1

This program would first apply the identity function to the argument, **1**, and then apply the **Increment** function to the result of the identity function yielding **2**.

The simulator also has a library facility which allows a collection of pre-defined functions to be created and named for later use. Such functions are defined by using the following syntax:

where <function\_name> is the name of the function and <BMF\_Expression> is the definition. To use the newly defined function in subsequent code, it is referenced by its name, prefixed with a dollar symbol. As an example, the following function could be defined thus:

and then referenced by using \$Trivial. When such a predefined function is used, the semantic meaning is equivalent to textual substitution of the function reference by its

defining BMF expression. As such, the library mechanism is a facility to assist in the development of programs and in no way affects the referential transparency of the BMF code. That is to say, once a library function is assigned to a name, the same function will always be associated with that name; there is no dynamic reassignment or levels of scope.

## 2.4 Data Types

The following data types define the entities that may be used as input to, and appear as output from, BMF programs. The simple data types are: Integers, Real Numbers and Booleans.

#### 2.4.1 Lists

A list or vector is an ordered collection of zero or more items of the *same* type. Syntactically, a list is a comma separated list of items enclosed by square brackets. i.e.

$[a_1, a_2, \ldots, a_n]$

The empty list is denoted by [].

#### 2.4.2 Tuples

Tuples are a collection of one or more items that may be of different types. Syntactically, a tuple is a comma separated list of items enclosed by braces. i.e.

$\{a, b, c\}$

where a, b, c can be different types.

## 2.5 Program Constructors

#### 2.5.1 Composition

In BMF, a program consisting of a sequence of operations is expressed as a composition of functions. The B\_Comp operator, introduced previously, provides this facility. From an operational viewpoint, a composition of two functions takes the output of the first function and pipes it as input into the second function. In more precise terms, if we have the functions F and G applied to an argument, x, then:

$B_Comp(F)(G) x \Leftrightarrow F(G(x))$

Expressing composition in this way can make programs more difficult to read. An infix  $\cdot$  is often used instead of B\_Comp when describing programs.<sup>2</sup>

$F.G \Leftrightarrow B\_Comp(F)(G)$

#### 2.5.2 All-Applied-To

As well as composition, another means of assembling functions in a program is by the use of the all-applied-to operators. There are two versions, B\_Allvec and B\_Alltup which use lists or tuples respectively.

#### **B\_AllVec**

This operator takes a list of functions, applies them to individual copies of the input argument, and returns a list containing the results. If  $f_n$  defines a function and x is an argument then:

B\_Allvec  $[f_1, f_2, ..., f_n] x = [f_1(x), f_2(x), ..., f_n(x)]$

$<sup>^{2}</sup>$  The two forms will be used interchangeably in this chapter, for the sake of clarity, but the infix form cannot be used as input to the simulator.

## **B\_AllTup**

B\_Alltup is very similar in operation except that it uses tuples instead of lists. Once again, if  $f_n$  defines a function and x is an argument then:

B\_Alltup

$$[f_1, f_2, ..., f_n] x = \{f_1(x), f_2(x), ..., f_n(x)\}$$

Notice that both B\_Alltup and B\_Allvec use square brackets to denote the input list or tuple respectively.

## 2.6 Constants

To generate an integer, real or boolean constant in a program, the B\_Con function is used. For boolean constants, B\_con takes the arguments B\_True or B\_False. For numerical constants, the value must be prefixed with the appropriate type identifier: either B\_Int or B\_Real.

## 2.7 Operators

The operations implemented in the source code have been broken up into two main groups: those appearing in the grammar under  $\langle b\_exp \rangle$ , called expressions, and those under  $\langle b\_op \rangle$ , sometimes informally referred to as 'operators'. The latter group, when used, are prefixed with the '**B**\_**Op**'. The constructs appearing under  $\langle b\_op \rangle$  can be conceptually divided into two groups, Unary or Binary 'Operators', depending on whether they operate on a single argument or a single tuple of two arguments (i.e. a pair) respectively<sup>3</sup>.

#### 2.7.1 Binary 'Operators'

These operators all require a 2-tuple of arguments on which to operate. They can be divided into three main categories:

<sup>&</sup>lt;sup>3</sup> The choice of which operators appear under B\_Op is largely based on historical considerations and may be varied in the future.

## Arithmetic

These operators provide the standard arithmetic operations and are denoted with the self-explanatory names of: B\_Plus, B\_Minus, B\_Times and B\_Divide. In this implementation, these operators are overloaded so that they may be used, transparently, with any combination of real and integer pairs. s an example of how a binary operator is used:

$B_Op(B_Plus) \{a, b\}$

would yield the result 'a+b'.

## **Boolean and Comparsion**

All the standard boolean and comparison operators are provided:

#### **Boolean Operations:**

B\_Neg, B\_And, B\_Or

**Comparison Operators:** (with their meaning shown to the right)

B\_Eq = B\_Gt > B\_Lt < B\_Le <= B\_Ge >=

These operators are also overloaded so that they may be used with any combination of integer and real arguments.

## **Aggregate Operators**

#### **B\_Index**

B\_Index takes a tuple containing a list and an integer, as input, and returns the list item indexed by the integer.

$$B_Op(B_Index) \{ [A_0, A_1, ..., A_I ... A_N], I \} = A_I$$

#### **B\_Project**

P\_Project re-orders a list according to a vector of index values thus allowing an arbitrary permutation of the list item to be performed. The first argument is the list to be projected. The second argument contains a list of indices: the index at each position in this list indicates which item of the input list is to go in that position.

$B_Op(B_Project) \{ [A_0, A_1, ..., A_N], [I0, I1, ..., IN] \} = [A_{I0}, A_{I1}, ..., A_{IN}]$

#### **B\_Distl**

B\_Distl takes in a pair consisting of a data item and a vector and distributes the data item over the vector in a pair-wise manner.

$B_Op(B_Dist) \{X, [A_0, A_1, ..., A_N]\} = [\{X, A_0\}, \{X, A_1\}, ..., \{X, A_N\}]$

where X can be any data item including another list or tuple.

#### 2.7.2 Unary Operators

#### **B\_Neg**

This operator performs negation on a boolean or numerical argument.

#### **B\_Length**

Takes a list as an argument and returns its length.

#### **B\_Iota**

B\_Iota takes an integer argument, N, and returns the list [0, 1, 2, ..., N-1]

#### 2.7.3 Aggregate Operators over Lists

#### **B\_Map**

Map applies a function to every element of the input list. So if f is a unary<sup>4</sup> function then map can be defined as:

$$B_Map(f) [A_0, A_1, ..., A_N] = [f(A_0), f(A_1), ..., f(A_N)]$$

#### **B\_Reduce**

Reduce takes in an associative operator and default value and then effectively inserts the operator between the list items. The operator is then applied thus folding the list back to a single value. If  $\oplus$  is an associative operator and X the default value then:

**B\_Reduce** (

$$\oplus$$

) (X) [A<sub>0</sub>, A<sub>1</sub>, ..., A<sub>N</sub>] = X  $\oplus$  A<sub>0</sub>  $\oplus$  A<sub>1</sub>  $\oplus$  ...  $\oplus$  A<sub>N</sub>

and:

B\_Reduce  $(\oplus)(X)[] = X$

The Reduce implemented here, and that implemented in the Adl project<sup>5</sup>, makes no attempt to verify the associativity of the operator used. Additional forms of Reduce can be defined (as in the Adl project), such as directed left and right reductions[3, 8] which can use associative or non-associative operators - such variations are, however, inherently sequential.

#### Zip

Zip operates on a pair of lists merging them, in a pair-wise fashion, using a binary operator. If  $\oplus$  denotes a binary operator then:

Scan

<sup>&</sup>lt;sup>4</sup> By 'unary' in this context, we mean a function that operates on a single argument: eg. B\_Neg, \$Increment etc. - NOT a function that takes a single tuple of two arguments like, say: {a,b}

<sup>&</sup>lt;sup>5</sup> In the Adl project, this type of reduce is called 'B\_ReduceP'

Scan is also known as prefix or accumulate. From an operational viewpoint, scan can be viewed as the mapping of a reduction over the initial sub-lists of the input. That is, if  $\oplus$  denotes an associative operator then:

#### Split

The Split operation takes in an integer argument, P, and transforms the input list into a list of P sub-lists.<sup>6</sup> In performing the split, the data is partitioned as evenly as possible to make the sub-list lengths uniform.<sup>7</sup> As an example, if P = 3 and list length is divisible by P then all the sub-lists will be of equal length:

B\_Split (B\_Num 3) [1, 2, 3, 4, 5, 6] = [[1, 2], [3, 4], [5, 6]]

Alternatively, if the list length is not divisible by P then the first sub-list will be one item longer than the rest:

B\_Split (B\_Num 3) [1, 2, 3, 4, 5, 6, 7] = [[1, 2, 3], [4, 5], [6, 7]]

which still yields the most even distribution possible.

### 2.8 Parallel BMF Code

On of the primary advantages of BMF is that it enables the expression of a wide variety of parallel algorithms through the use of a small number of fundamental constructs: the parallel constructs are, in fact, data-parallel interpretations of serial aggregate operations, namely: Split, Map, Reduce, Scan, Zip, Distl and Project.

<sup>&</sup>lt;sup>6</sup> It Should be noted that the split operation described here is quite distinct from the version introduced by Bird in  $\{[8] p171\}$  which splits a list into its head and tail components.

<sup>&</sup>lt;sup>7</sup> Chapter 5 will describe the partitioning algorithm in detail.

Having relatively few, but highly expressive, parallel constructs not only reduces the cognitive burden on the programmer, but also increases portability because there are fewer parallel operations that need to be specifically implemented on the target architecture.

The parallel versions of the aggregate operators are distinguished from their serial counterparts by being prefixed with a 'P'. The list is the fundamental data-structure in parallel BMF, it being the only one that can be distributed across a machine.<sup>8</sup> In the following sections, the processor on which a particular list element resides will be labeled by a superscript; this is done to illustrate the operation of parallel BMF code but such information is not required by the programmer in designing the code.

From the programmer's point of view, the parallel versions of the aggregate operations have the same semantic meaning as their serial counter-parts except that the operations occur over distributed data; as a result, although the programmer has to use the appropriate operations, details of how the data is mapped and distributed onto the target machine are completely hidden. That is to say, a BMF program has the same semantic meaning whether it is expressed in terms of serial or parallel constructs. To illustrate this point, and to introduce the nature of parallel BMF program, consider the following example:

If we start with the list [1, 2, 3, 4, 5, 6] and split it three ways:

B\_Split (B\_Num 3) [1, 2, 3, 4, 5, 6] = [ [1, 2], [3, 4], [5, 6] ]

we can now increment each list item by mapping the map of the increment function over the list.

```

B_Map (B_Map ($Increment)) [ [1, 2], [3, 4], [5, 6] ]

= [ [2, 3], [4, 5], [6, 7] ]

```

On the other hand, if we were to distribute the input list over the machine using P\_Split:

<sup>&</sup>lt;sup>8</sup> We will see later that the P\_Distl operator can distribute a scalar across the machine but only across an already distributed vector.

where each sub-list is now on a different processor, as indicated by the superscripts, we would use a parallel map of the serial map of the increment function

where the parallel map has the same semantics as the serial one except that it can operate on a distributed list.

As can be see from this example, the only difference between the two programs is that the outer map is either the serial or parallel version, as appropriate.

## 2.9 Parallel Operators

Having now seen an example of parallel BMF code, this section will describe, in qualitative terms, the parallel operators available in this implementation. A more detailed and precise account of their operation, and the trace results that they produce, will be given in Chapter 5.

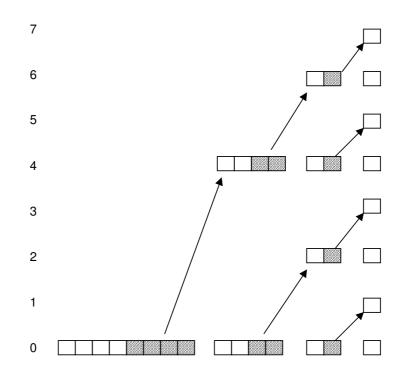

#### 2.9.1 P\_Split

The split operation is the primary means by which data is spread across the machine. Like its serial counter-part, P\_Split partitions an input vector into a list of sub-lists except that each sub-list is sent to a different processor. P\_Split takes in two integer arguments, the first indicates the number of processors over which to spread the data and the second sets the stride (the distance between two adjacent processors). The stride argument is  $\log_2$  of the actual stride; in this way, the stride is quantized to a power of two. The stride refers to the difference in processor id's between adjacent

list nodes after the completion of the split operation<sup>9</sup>. For a three way split with a stride of 1 ( $1 = 2^{0}$ ):

#### 2.9.2 P\_Map

P\_Map is semantically equivalent to the serial version except that it can operate on a distributed list. Map is particularly efficient in the sense that it does not involve any data exchange between the processors.

#### 2.9.3 P\_Reduce

P\_Reduce can be viewed (informally) as being the opposite of the P\_Split operation because it allows a distributed list to be collected back together onto a single processor through the use of an associative operator<sup>10</sup>. From the programmer's point of view, it works in exactly the same way as B\_Reduce except that no default value is required<sup>11</sup>. P\_Reduce is commonly used with the list concatenate operator, B\_Conc to gather a split list of sub-lists back to a single processor. For example taking the distributed list from the last example, we could gather it back to processor zero again by:

The associativety of the operators used with P\_Reduce allow the evaluations to occur in an arbitrary order without affecting the result: this fact permits P\_Reduce to conduct many of the evaluations in parallel thus allowing the operation to be completed in  $\log_2 N$  operations where N is the number of items in the list.

<sup>&</sup>lt;sup>9</sup> The stride argument, and how it is used to facilitate nested splits will be described in section 5.3.

<sup>&</sup>lt;sup>10</sup> Reduce with concatenate is often used after the parallel processing of a split list - such an operation is *not* the inverse of split, however, because the information regarding the lengths of the sub-lists is lost.

<sup>&</sup>lt;sup>11</sup> This is assuming that there are at least two processors over which to reduce

#### 2.9.4 P\_Scan

P\_Scan, like P\_Reduce, operates on a distributed list except that the results is still a distributed list. As in the case of P\_Reduce, the associativity of the operator used allows the development of an algorithm that can perform the scan in  $log_2N$  steps.

#### 2.9.5 P\_Zip

P\_Zip, like B\_Zip, merges a pair of lists in a pair-wise fashion, using a binary operator. The two lists are distributed and must be conformable which is to say, they must be the same size and mapped across the same set of processors; this ensures that the two components of each 'evaluation pair' reside on the same processor so the 'zipping' operation can occur in parallel with no inter-processor data transfer. If  $\oplus$  denotes a binary operator and A and B are a pair of distributed lists then:

P\_Zip (⊕) { [

$$A_0^{0}, A_1^{1}, ..., A_N^{N}$$

], [ $B_0^{0}, B_1^{1}, ..., B_N^{N}$ ] }

= [ ( $A_0 \oplus B_0$ )<sup>0</sup>, ( $A_1 \oplus B_1$ )<sup>1</sup>, ..., ( $A_N \oplus B_N$ )<sup>N</sup> ]

Notice that each pair of list items in parenthesis reside on a separate processor so the evaluations can occur in parallel.

## 2.9.6 P\_Distl

P\_Distl is used to broadcast an item from one processor to many by sending the item to each node of a distributed list. Let X be any data item and A be a distributed list, then:

#### 2.9.7 P\_Project

P\_Project re-orders a distributed list according to a vector of index values. Whenever a list item changes position, an inter-processor data exchange will occur. For example:

P\_Project { [ 0, 1, ..., N],

$$[A_0^0, A_1^1, ..., A_N^N]$$

} =  $[A_0^0, A_1^1, ..., A_N^N]$

would produce no data exchange because the position of each list element remains unchanged whereas:

P\_Project {

$$[A_0^{0}, A_1^{1}, ..., A_N^{N}]$$

,  $[N, N-1, ..., 1, 0]$  }

=  $[A_N^{N}, A_{N-1}^{N-1}, ..., A_1^{1}, A_0^{0}]$

affects a complete reversal of the list and will involve N data-exchanges.

## 2.10 Parallelisation of Serial BMF Code

In addition to providing a solid basis with which to express parallel algorithms, the formal framework of BMF provides a mechanism with which to parallelize serial code using a mathematical transformation process. The automation of such a process, as indicated in Chapter 1, appears to be intractably difficult except in the case of small, simple programs, or in programs displaying general, easily recognisable features. This section will give a brief introduction to the parallelisation process for some very simple BMF code to give some idea of the techniques involved.

Consider the problem of finding a series of factorials from Factorial(1) through to Factorial(N). Assuming that the Factorial function has already been defined, the following code would produce the required series:

B\_Map (\$Factorial) [1, 2, 3, ... N]

To transform this serial program into a parallel version over P processors, the following BMF identity will be made use of:

Informally, the Split-Property states that if a list is distributed using split and then reduced back again using concatenate, there is no net change in the data; that is, the net effect is equivalent to the application of the identity function.

Given this fact, a program can be composed with a split followed by a reduce with concatenate without affecting the result. Therefore the program becomes:

B\_Map (\$Factorial) . P\_Reduce ( B\_Op ( B\_Conc ) . P\_Split (B\_Num P ) (B\_Num 0 )

A further property can now be made use of:

$$B_Map (F) . P_Reduce (B_Op (B_Conc))$$

$$= P_Reduce (B_Op (B_Conc)) . P_Map (B_Map (F))$$

Applying Map-Promotion to the Factorial program yields:

P\_Reduce (B\_Op (B\_Conc) ) . P\_Map (B\_Map (\$Factorial) ) . P\_Split (B\_Num P) (B\_Num 0)

which is the final parallelized version. This example showed how parllelization can be performed through the application of a series of algebraic identities, specifically the Split-Property and Map-Promotion. Clearly a program of this size can easily be parallelized by inspection but for more realistically sized programs, the parallelization process becomes much more difficult.

## 3. Visualisation Methodology

## 3.1 Introduction

Having described the nature of the BMF source code in the previous chapter, the discussion will now turn towards what can, in some sense, be regarded as the target code of the simulator; namely the PICL format tracefile and the associated visualisation environment. This chapter will describe the relevant features of the PICL format, how it is used to record events in this project, and the inter-relationships between PICL and the visualisation package, Paragraph.

## 3.2 PICL

PICL [22] stands for 'Portable Instrumented Communication Library' and as its name suggests, not only defines a tracefile format, but also a generic message-passing library. The idea is that programs can be written using the generic PICL routines, rather than platform specific commands; this results in code that is more portable because it can be compiled and run on any architecture on which the PICL library has been implemented. PICL also provides tracing facilities so that any program that makes use of the generic routines can produce trace information automatically without having to modify its source code; this has the obvious advantage of eliminating the dangers involved with the manual insertion of instrumentation code throughout a potentially complex program. In this project, only the trace format of PICl is used as the trace events are generated directly by the simulator.

#### 3.2.1 PICL Tracefile Format

The tracefile format provides a very general and extensible framework with there being a number of pre-defined trace events as well as facilities which enable customized 'user' events to be added. Some of the pre-defined events include categories such as: Inter-Process communications, Synchronization, File I/O and Resource Allocation. In this project, however, only a sub-set of the available events was required and will be described here. The PICL Documentation[22] contains the details for all the PICL events.

#### 3.2.2 Basic Trace Record Structure

The tracefiles are written as an ASCII file with one trace record per line. Each trace record consists of a sequence of space separated ASCII fields all of which must appear on the same line. There are six basic fields which all records must contain:

## 1. Record Type:

This field is either '-3' indicating the entry (beginning) of an event or '-4' which denotes the exit (end) of an event.

## 2. Event Type:

This indicates the type of event that is being traced. The events that are used in this project are:

- -21 Non-blocking send

- -51 Blocking receive

- -601 Processor has become idle.

A more detailed description of these events will appear below

## 3. Time Stamp

A floating point number which indicates the time at which the event occurred.

## 4. Processor Id

The Id of the processor on which the event occurred

## 5. Process Id

The process in which the event occurred. At present, neither PICL nor Paragraph support more than one process per processor. As a result, this field is always '-1' which refers to all processes on a given processor. (So in this case, -1 refers to the one and only process).

## 6. Number of Event Specific Data Fields

This field is an integer indicating how many event specific data fields follow. The number and nature of these fields is dependent on the *event type*; they are described in the next section.

When there are one or more event specific data fields (i.e. Field six is greater than zero), the following data descriptor is present to indicate the type of data contained in them:

## **Data Descriptor**

The available types and the associated designator are:

- 0 Character

- 1 String

- 2 Integer

- 3 Long Integer

- 4 Single Precision Floating Point

- 5 Double Precision Floating Point

In this project, only integer data is required and so this field is always set to '2' After the data descriptor, the event specific data fields follow.

## 3.2.3 Events and Event Specific DataFields:

The PICL events used in the project along with the interpretation of the specific data fields (if any) are shown below. The numbers is parenthesis are first two basic fields which identify the event.

## Start Non-Blocking Send (-3 - 21)

This event corresponds to a processor beginning to move data into the network; as such, any time between this event and event (-4 -21) is considered to be communications overhead.

#### **Data Fields:**

• Message Length in Bytes: The length of the message sent.

- *Type*: The type of the message expressed as an integer. This field allows different types of messages such as control versus data packets to be distinguished. In this implementation, the type is always '1'.

- *Destination Processor ID*: The processor to which the message is sent.

## End Non-Blocking Send (-4 -21)

This event occurs when the transfer of data into the network, started by event (-3 -21), has been completed. This event has no extra data fields.

## Start Blocking Receive (-3 -51)

Denotes a processor waiting for the arrival of a message. This is a blocking receive and so all the time between this event and the reception of the message (event -4 -51) is counted as communications overhead.

### **Data Fields:**

• *Requested Type*: The type of message that is expected to be received.( Always '1' in this implementation).

## End Blocking Receive (-4 -51)

Denotes the arrival of the message which was initiated by event (-3 -51).

#### **Data Fields:**

- Message Length: Number of bytes received.

- *Type of message received*: Always '1' in this implementation.

- Source Processor: Processor from which the data was sent.

## Start Processor Idle (-3 -601)

This event occurs when the processor becomes idle.

## End Processor Idle (-4 -601)

Occurs when the processor becomes Busy (not idle).

#### 3.2.4 Example PICL Trace Records

Consider the following trace record:

The first six numbers correspond to the basic fields described in section 3.2.2. They can be interpreted as:

-3 -51 : The event is the start of a send

4.500 : The Send began at time 4.500 seconds

- 4 : Processor 4 is sending

- -1 : Process identifier which is always -1

- 3 : There are three event specific data fields following

- 2 : The type of the event specific data fields is Integer

The last three numbers are then the expected event specific data fields whose meanings are described in section 3.2.3

- 2 : The message being sent is two bytes long.

- 1 : The type of message being sent is one.

- **6** : The message is being sent to processor 6.

As another, simpler example:

-3 -601 5.000 12 -1 0

means that processor number twelve became idle at time 5.000 and conversely:

-4 -601 6.000 12 -1 0

indicates that processor twelve became busy (not idle) at time 6.000.

Notice that in this example, there are no event specific fields for event -601 as indicated by the zero in the last field.

## 3.3 The Trace Module

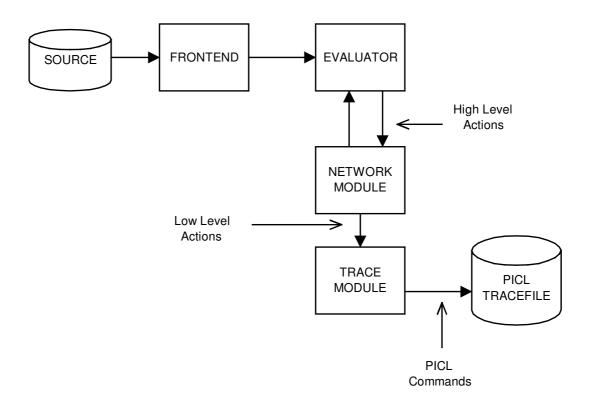

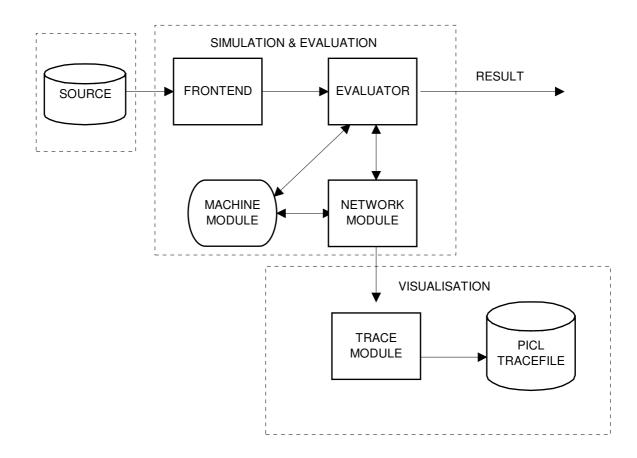

This section will describe the Trace Module which is the interface through which the rest of the simulator writes the tracefile. Figure 3-1 below, shows the logical structure of the simulator.

#### Figure 3-1: Logical Structure of Simulator

From a high-level point of view<sup>12</sup>, the operation of the simulator can be briefly described as follows: the source code is read in by the front-end, parsed, and then feed to the Evaluator. The Evaluator simulates the parallel execution of the code, interacting with the network module whenever inter-processor communications or changes in processor state<sup>13</sup> occur through a set of 'High-Level' actions described in Chapter 5. The network module then, in turn, generates an appropriate sequence of

<sup>&</sup>lt;sup>12</sup> The design and operation of the simulator will be discussed in detail in Chapter 5.

<sup>&</sup>lt;sup>13</sup> That is, when a processor changes from being Busy to Idle or vice versa - see section 3.4.1 for more details.

low-level trace events which are converted to PICL and written to the tracefile by the Trace Module. The Trace Module provides an abstract interface to the PICL tracefile format by providing a procedural 'wrapper' for each trace event. Below is part of the Ada[7] specification for the Trace Module:

procedure Begin\_Send (P\_Id : Integer ; Time : Float ; Size : Integer ; Ty : Integer; Dest\_Id : integer); procedure End\_Send (P\_Id : Integer ; Time : Float); procedure Begin\_Recieve(P\_Id : Integer ; Time : Float ; Ty : integer); procedure End\_Recieve(P\_Id : Integer ; Time : Float ; Size : Integer; Ty : Integer ; Source\_Id : Integer ; Time : Float); procedure Start\_Idle(P\_Id : Integer ; Time : Float); procedure Stop\_Idle(P\_Id : Integer ; Time : Float);

As can be seen, there is a procedure corresponding to each of the PICL events described in section 3.2. Each procedure simply takes in the required data as parameters and writes the appropriate ASCII sequence to the tracefile. For example the following call:

Begin\_Receive(4, 6.000, 1)

would generate the following PICL sequence:

-3 -51 6.000 4 -1 1 2 1

and

Start\_Busy( 2, 3.500 )

would generate:

-4 -601 3.500 2 -1 0

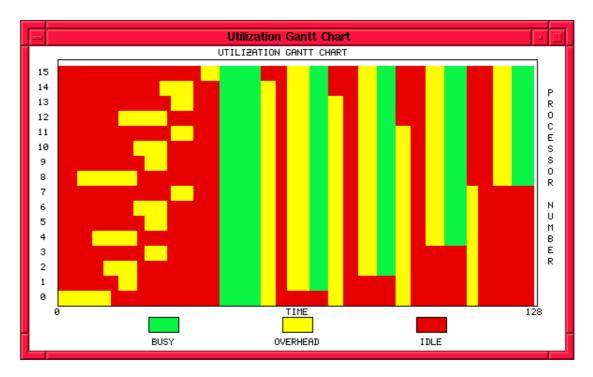

## 3.4 Paragraph

Paragraph[10, 11, 12] is a software package which provides facilities for the visualisation of trace information written in the PICL format. Although Paragraph was originally designed to visualize programs instrumented with the PICL library, there is no reason why it cannot be used with a PICL tracefile generated by some other means. This is the approach taken in this project where the PICL tracefile is generated by the simulator itself.

#### 3.4.1 Events

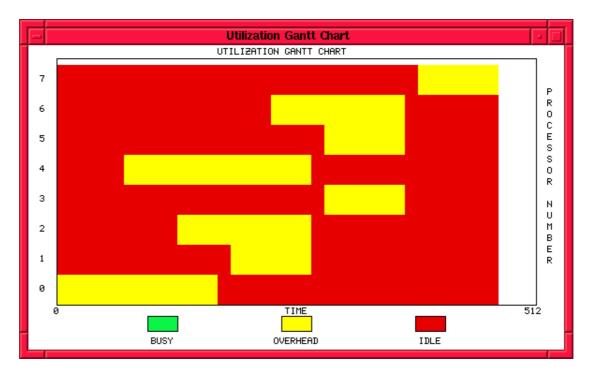

The events occurring on a parallel machine which are relevant to Paragraph can be divided into two categories: Changes in the state of each processor and inter-processor communications.

## **Changes in Processor State**

At any given time, each processing node of a parallel machine can be regarded as being in one of three mutually exclusive states: *busy, overhead* or *idle*. When Paragraph is used to visualize 'real' programs, a processor is said to be idle if waiting for the arrival of a message, in overhead if it is executing in the communications subsystem but not waiting for a message, and busy if doing anything else. So under this (default) scheme, a processor that is performing useful<sup>14</sup> computation and one which is occupied with non-communications overheads or sitting idle because it has nothing to do are all indistinguishable. In other words, a processor which is Busy has the *potential* to do useful computation, in that it is not occupied in the communications subsystem, but may not necessarily be doing so. Such a definition is used because the determination of whether a processor is doing useful computation or something else is considered to be too invasive<sup>15</sup>.

<sup>&</sup>lt;sup>14</sup> By useful, it is meant any computation which is required by the algorithm of the program.

<sup>&</sup>lt;sup>15</sup> i.e. Such a measurement would cause an unacceptable perturbation and affect the accuracy of the overall tracing process.

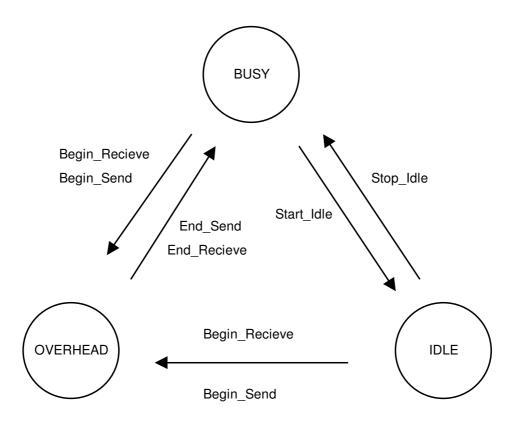

In this project, as the tracefile is generated directly by the simulator, a more intuitive set of definitions can be used:

### **BUSY:**

When the processor is actually performing useful computation.

#### **OVERHEAD:**

Time when the processor is processing communications overheads.

#### **IDLE:**

Anytime the processor is sitting idle either because it has nothing to do, or is it waiting for a message to arrive from another processor.

The relationships between the three states and the PICL commands which cause the various transitions are summarized in Figure 3-2.

Figure 3-2: Processor State Transition Diagram

From the above diagram, it can be seen that to put the processor back into the Idle state, a Start\_Idle command must be issued after every End\_Receive, End\_Send and at the completion of a computation.

## **Inter-Processor Communications**

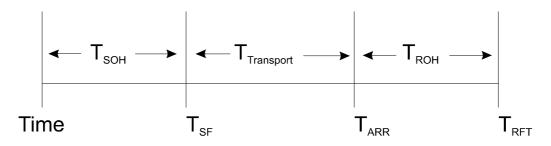

Inter-processor communications are characterized, in this project, by three phases:

## Send

During this phase, the source processor transfers the data to be sent into the network buffer. This period is begun with a Begin\_Send and ended with End\_Send.

## Transport

The transport time is the time taken for the message to travel through the network to the destination processor. During this phase, the destination processor remains idle and so no additional trace commands are issued.

## Receive

Once the message has arrived at the destination processor, it is transferred from the network buffer. A Begin\_Receive is issued at the start of the transfer and an End\_Receive upon completion.

## 3.5 Paragraph Examples

To demonstrate how the events described in the previous section relate to the actual visualisation displays produced by Paragraph, consider the following, simple example:

We have a four processor machine with the processor Id's running from zero to three. A single inter-processor send occurs, at time 1.0 from processor 0 to processor 2. Upon receiving the message, processor 2 then operates on the data for 5 time units. An appropriate sequence of trace events describing this situation could be:

| 1 | <pre>start_Idle(0, 0.0);</pre> | {Set all Processors to idle |

|---|--------------------------------|-----------------------------|

| 2 | <pre>Start_Idle(1, 0.0);</pre> | state}                      |

| 3 | <pre>Start_Idle(2, 0.0);</pre> |                             |

```

4

Begin_Send(0, 1.0, 5, 1, 2); {Initiate send from 0 to 2}

5

End_Send(0, 2.0);

Start_Idle<sup>16</sup>(0, 2.0);

{Enter idle state again}

6

{The gap in time here represents the transport time

through the network}

7

Begin_Recieve(2, 4.0, 1);

{Begin receiving data}

8

End_Recieve(2, 5.0, 5, 1, 0);

9

Stop_Idle(2, 5.0);

{Begin computation}

10

Start_Idle(2, 10.0);

{Finish computation}

```

If the resulting PICL tracefile for this example is fed into Paragraph, the following displays would be generated:

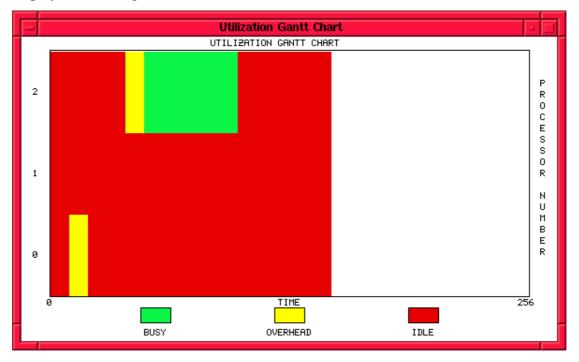

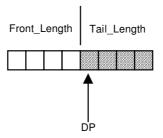

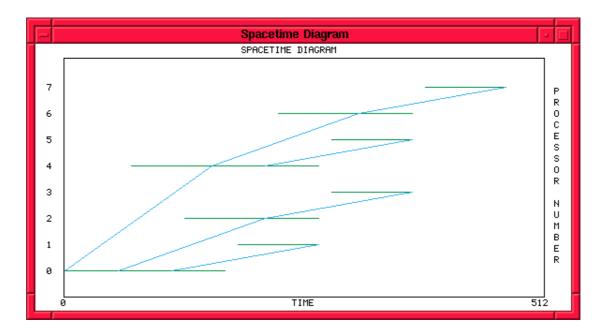

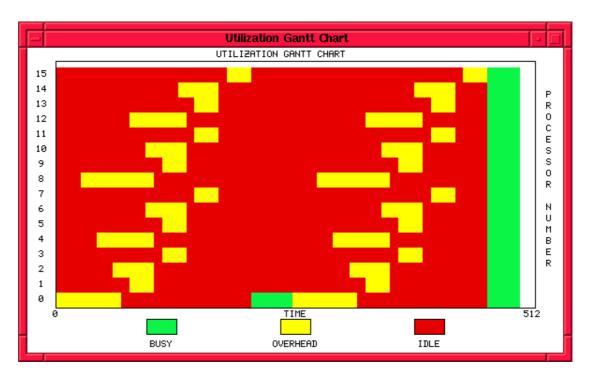

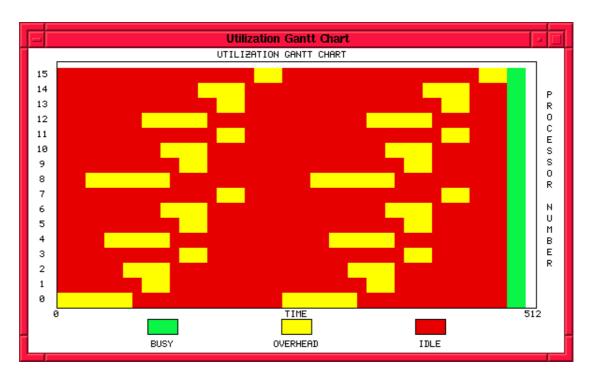

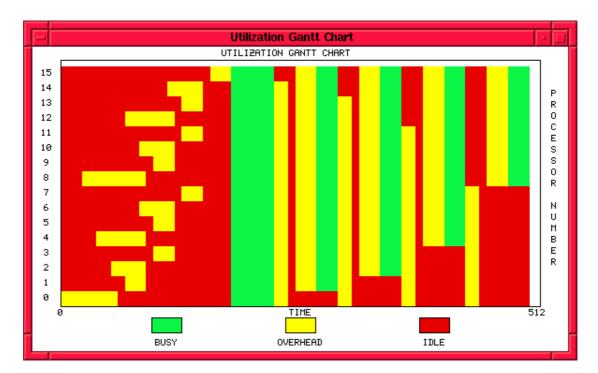

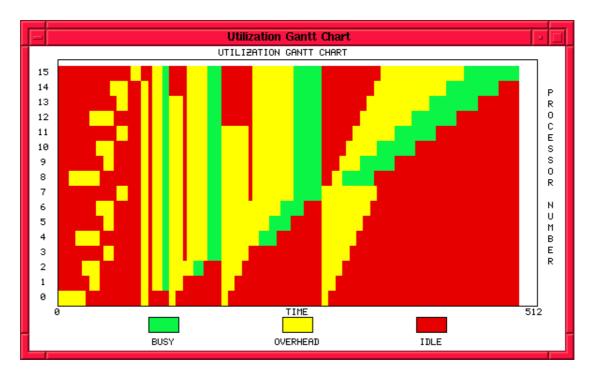

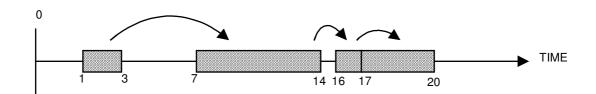

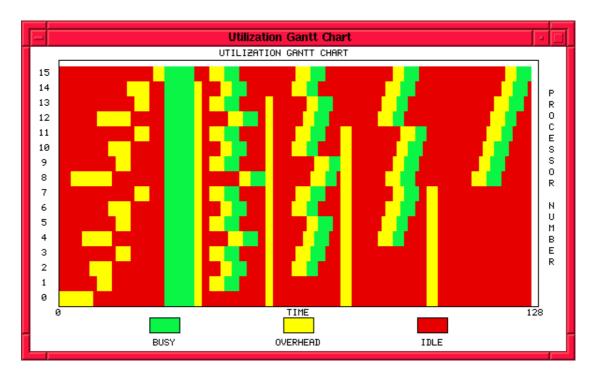

**Figure 3-3: Example Gantt Chart**

This display is called a 'Gantt Chart' and shows, at any given time, which of the three states each processor is in according to the colour. The correspondence between this display and the example can be seen as follows: all of the processor are in the idle state until processor 0 starts sending (line 4). Then there is a gap, in time, between

<sup>&</sup>lt;sup>16</sup> Notice the Start\_Idle here to prevent Paragraph from returning the processor to the Busy State. - see figure 3-2.

processor 0 finishing the send(line 5) and the message arriving at processor 2 (line 7). Processor 2 then finishes reading in the message(line 8) and enters the Busy state for five time units (lines 9 & 10).

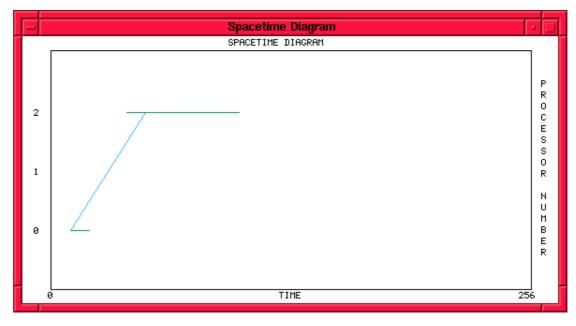

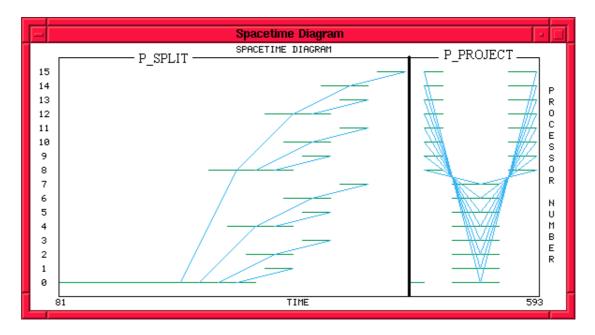

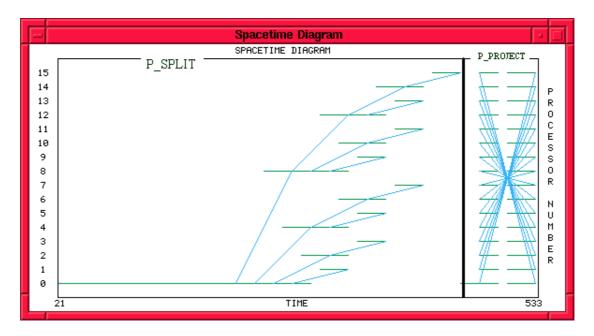

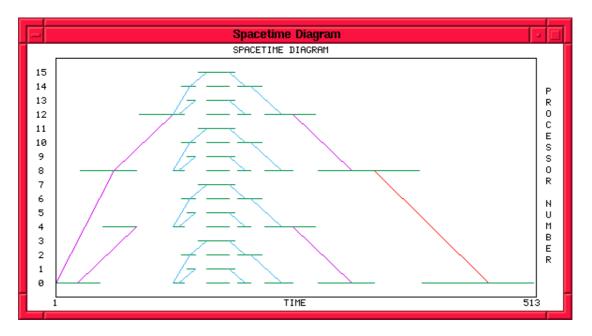

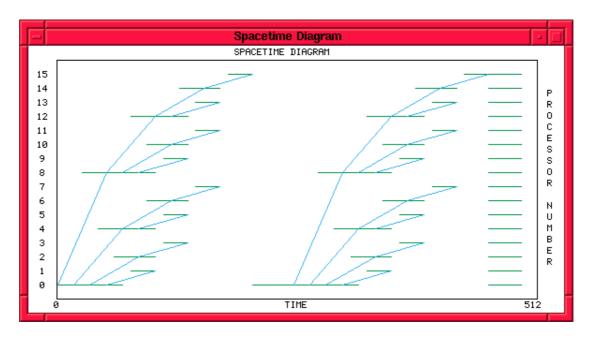

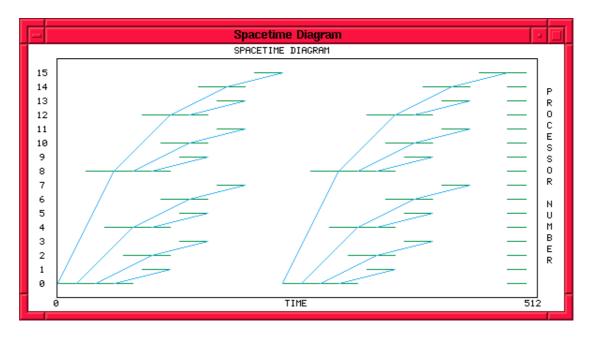

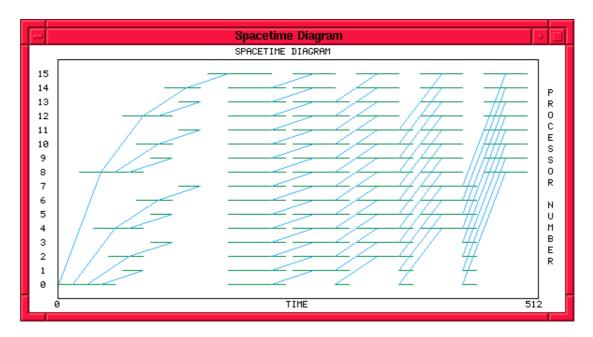

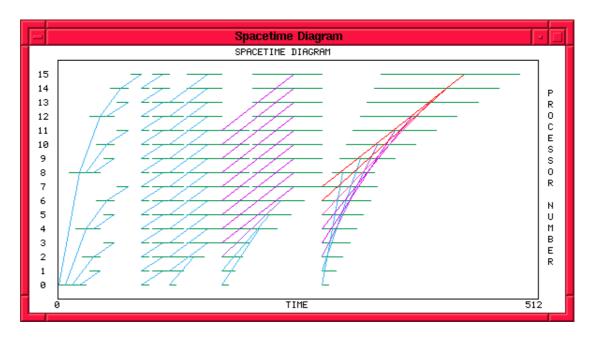

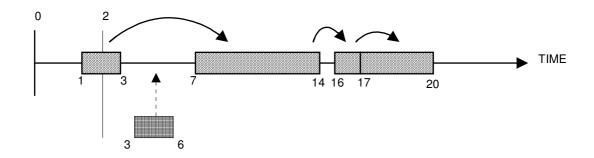

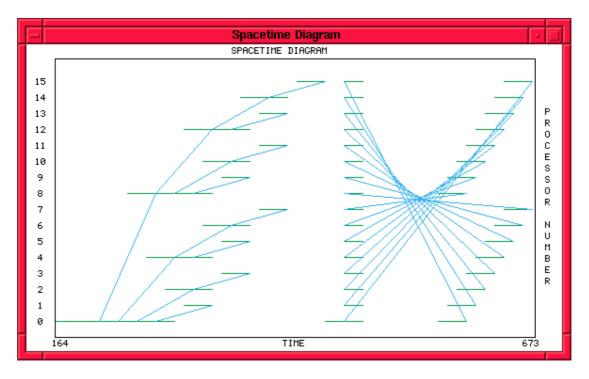

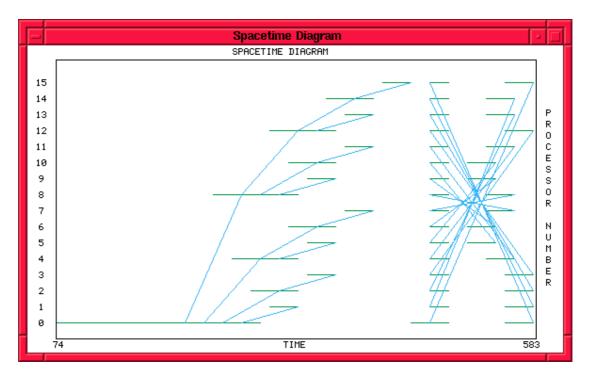

Figure 3-4: Example Space-Time Diagram

The Space-Time diagram is useful for visualizing the patterns of inter-processor communications. Whenever an inter-processor communication occurs, a line appears between the two processors starting at the beginning of the send (event -3 -21) to the completion of the receive (event -4 -51). Being a space-time diagram, for a given inter-processor distance, the steeper the line, the faster the communication was. The lines are also colour coded according to how large each message was. The horizontal lines correspond to times where the processor is either busy or in overhead. Looking at figure 3-4, the pattern shown clearly corresponds to that of the Gantt chart in figure 3-3; in particular, notice that the horizontal lines show the overheads involved

in the send and receive with the line of processor 2 extending beyond the completion of the receive due to the extra Busy time.

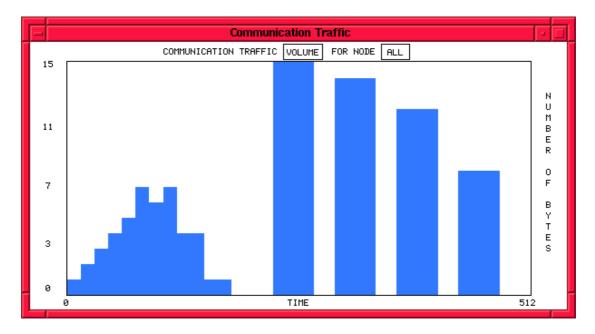

Paragraph provides a number of additional displays which look at the same data, but from different point of view. Examples of the other displays will appear in chapters 5, 6 & 7 and their function will be explained there. The Paragraph manual[12] also provides a comprehensive overview of the available facilities.

# 4. The Parallel BMF Simulator

# 4.1 Overview

Figure 4-1 provides a logical overview of the simulator, separated into three areas. Having described the Source code and Visualisation Methodology previously, the present chapter will focus on the design and implementation of the core components of the simulator namely, those categorized in the diagram as Simulation & Evaluation. Together, these components encompass the entire functionality of the simulator save the final translation of the trace events into PICL which is performed by the Trace Module described in chapter 3.

Figure 4-1: Logical Structure of the Simulator

## 4.2 Implementation of Datatypes

The data-types supported in this implementation can be divided into two main groups: simple types and aggregate structures. The simple types consist of integers, reals and booleans and the aggregates consist of the list and tuple structures.

## 4.2.1 Lists and Tuples

The representation of the list and tuple structures are very similar with both being implemented as a linked list of variant records [7]; the use of variant records allows lists and tuples of any (BMF) type to be represented. For example, consider the node definition of the list structure :

```

type List_Node(Selector: Lnode_Type := Integer_ty) is record

Next : List := null;

Proc_Id : Integer := 0;

case selector is

when list_Ty =>

List_Val : List := null;

when Tuple_Ty =>

Tuple_Val : Tuple := null;

when Integer_Ty =>

Integer_Val : Integer := 0;

when Real Ty =>

Real_Val : Float := 0.0;

when Bool_Ty =>

Bool_Val : Boolean := False;

end case;

end record;

```

#### Figure 4-2: Ada List Node Definition

From this, it can be seen that through the choice of the appropriate selector, a list node can contain any of the BMF types including another list or tuple. A number of functions were written to work with and manipulate the tuple and list structures including, for example, functions to: find the length of a list, perform indexing, appending etc.

#### 4.2.2 Values

To accommodate arbitrary BMF programs, the evaluator (described later) must be polymorphic in the sense that it can accept programs which may return any BMF type and also accept any BMF type as an argument. To achieve this, all BMF data both arguments and function results are wrapped within the following variant structure called a Value:

```

type Value(Selector: Lnode_Type := Integer_Ty) is record

Proc_Id : Integer := 0;

case selector is

when list_Ty =>

List_Val : List := null;

when Tuple_Ty =>

Tuple_Val : Tuple := null;

when Integer_Ty =>

Integer_Val : Integer := 0;

when Real_Ty =>

Real_Val : Float := 0.0;

when Bool_Ty =>

Bool_Val : Boolean := False;

end case;

end record;

```

#### Figure 4-3: Ada Value Specification

As in the case of list and tuple nodes, by the appropriate choice of the variant, Selector, a Value can contain data of any BMF type. It should be noted, that by using such a representation, any type checking that is performed has to be provided by each sub-evaluator<sup>17</sup> prior to the application of each operation. In this implementation, argument type checking is carried out for a few operations such as, for example, B\_Length (checks for a list argument) and the boolean operators (checks for a tuple of booleans). It is anticipated that the simulator will primarily be used with automatically generated code which should already have appropriate typing thus negating the need, at this stage, for extensive argument checking to be performed.

<sup>&</sup>lt;sup>17</sup> Section 4.5 covers the evaluator.

## 4.3 Front End

The 'front end' consists of the a scanner and a parser whose function is to convert the ASCII source code, representing a BMF program and its argument, into an abstract representation suitable for evaluation.

#### 4.3.1 Scanner

The purpose of the scanner is to convert the ASCII source code into a stream of tokens which can then be processed by the parser. A token may be a 'reserved word' (such as B\_Id, B\_Map etc.), a special symbol such as a '(' or '[', or a literal value such as an integer, real or boolean.

#### 4.3.2 Parser

The parser uses the stream of tokens from the scanner to construct an abstract syntax tree representing the program and in doing so, also checks the code for syntactic correctness. The design of the parser is based on the recursive descent method which is both easy to understand and implement, relatively efficient, and easily extendible. The recursive descent method fits in very naturally with the simple, non-ambiguous grammar of the source code<sup>18</sup>. On disadvantage of this parsing technique is that error recovery is more difficult than with table driven parsing but this is not a significant problem because it is anticipated that the simulator will work primarily with automatically generated code which should be correct.

Both the scanner and parser are sufficiently self-contained that they can be changed or modified to accommodate virtually any consistent form of source code notation without having to modify the rest of the system. For trivial changes such as, for example, changing the representation of the plus operation from 'B\_Plus' to '+', only the scanner needs to be updated. More extensive changes such as representing functional composition with an infix dot rather than the prefix 'B\_Comp'<sup>19</sup> would involve modification of the parser as well.

<sup>&</sup>lt;sup>18</sup> Looking at Appendix A, it is clear that the grammar is LL(1), which is to say that it can be deterministically parsed using only one look-ahead symbol.

$<sup>^{19}</sup>$  i.e. changing from the form B\_Comp (A) (B) to A . B

## 4.4 Internal Representation of BMF Programs

As mentioned previously a BMF program, once parsed, is represented by an 'abstract syntax tree' or 'parse tree'. The parse tree is implemented, literally, as a tree data structure with each node being polymorphic to accommodate the various BMF expressions (i.e. those constructs which appear under <b\_exp> in the grammar). As with data type representations, the polymorphism of the parse tree is implemented by the use of a variant record as shown in figure 4-4. The variant component of the parse tree node takes the value of the BMF construct which the node represents.

```

type Ptree_Node(Selector : Pnode_Type := B_Id) is record

case Selector is

when B_Map | B_Zip | P_Zip | B_Comp | B_Reduce | B_Scan |

B_Addr | P_Split | P_Reduce | P_Map |P_Scan =>

C1 : Ptree := null;

case Selector is

when B_Comp | B_Reduce | B_Addr | P_Split =>

C2 : Ptree := null;

when others => null;

end case;

when B_Alltup | B_Allvec =>

C : PList;

when B_Id | P_Distl | P_Project =>

null;

when B_Num =>

Integer_Val : Integer := 0;

when B_Con =>

Constant_Value : Constant_Record;

when B_Op =>

Operator : Operator_Type;

end case;

end record;

```

#### Figure 4-4: Ada Specification of Parse Tree Node

Looking at the node specification, it can be seen that the BMF constructs can be divided into several categories according to what information is contained within their parse tree nodes:

#### 4.4.1 Higher Order Constructs

In the current context, 'higher-order' constructs are defined to be those which take one or more other BMF expressions as arguments with each such argument being represented by a separate child parse tree. It should be noted that the standard definition of a 'Higher Order' function is one which takes another function as its argument; this is slightly different to the definition used here because operators such as B\_Addr have 'B\_Num' nodes as children but such nodes do not represent functions. The number of child parse trees may be one in the case of constructs such as B\_Map or two for constructs like B\_Reduce. The 'all-applied-to' operators (B\_Allvec and B\_Alltup), may have any non-zero number of arguments<sup>20</sup> and so have a list of child parse trees which may be of any length.

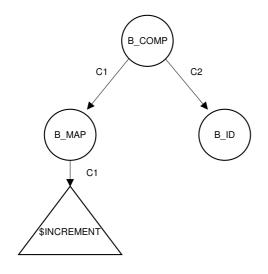

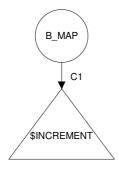

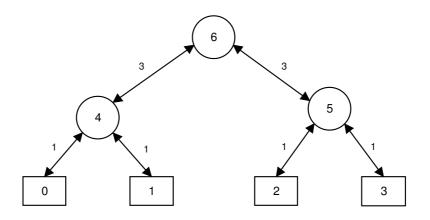

For example, the parse tree for the program:

B\_Comp (B\_Map ( \$Increment )) (B\_Id)

would appear, symbolically, as:

<sup>&</sup>lt;sup>20</sup> This is a slight simplification as B\_Allvec normally must have at least one argument and B\_Alltup, at least two.

where the triangle is the parse tree representing the \$Increment function and the arrow labels refer to the child designators shown in figure 4-4. Notice the B\_Id function, which is not 'higher-order', has no children.

#### 4.4.2 'Operators' under B\_OP

As mentioned previously, for historical reasons, some of the BMF constructs appear under the  $\langle b_op \rangle$  non-terminal in the grammar and are, therefore, prefixed in the syntax by 'B\_Op'. Such constructs are represented by a specific tree node type, 'B-Op', with the node containing the type of the operator under the field 'Operator'.

#### 4.4.3 Miscellaneous Constructs

There are several miscellaneous BMF constructs which do not fit into the two previous categories: B\_Id, P\_Distl and P\_Project have no associated extra information or children and so have a 'null' record entry. B\_Num nodes store an integer value in a field called 'Integer\_val' and B\_Con nodes store a 'Constant\_Value' which can be an integer, real, or boolean value.

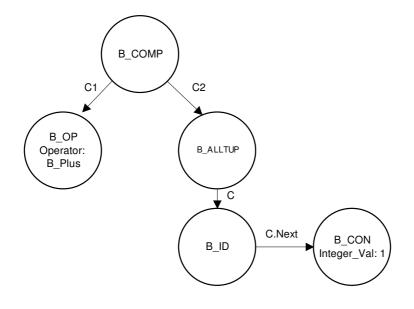

The use of the above elements are illustrated in the following example:

The \$Increment function, used a number of times previously, can be written:

\$Increment = B\_Comp (B\_Op (B\_Plus)) (B\_Alltup [ B\_Id, B\_Con (B\_Int

1)]))

when parsed, \$Increment can be represented by the following tree:

Notice how the B\_Op and B\_Con expressions contain the 'extra' information within the node ('B\_Plus' in the case of B\_Op and '1' is the case of B\_Con). Also of note is that the B\_Alltup node has a list of children with 'C' pointing to the first argument and 'C.next' referencing the second.

## 4.5 Evaluator

Once processed by the front-end, the parse tree representing the program is passed to the evaluator. The evaluator is, in many respects, the core of the simulator. It is responsible for the simulated execution of the parallel BMF code as well as, together with the network module, producing the necessary trace information reflecting any inter-processor communication and changes in processor state which may have occurred<sup>21</sup>. This section will concentrate on the evaluation methodology itself with the following two sections detailing the modeling of parallelism and the inter-connection network.

At the top level, the evaluator is invoked by a function call which has the following form:

Program\_Result := Eval (Pt, Arg)

where: Pt is the parse tree representing the program Arg is the argument of the program

Both Arg and Program\_Result are *Values*, as defined in section 4.2.2, to allow the evaluator to accept and return any BMF type. The Eval function effectively serves as an interface between the parser and sub-evaluators which perform the actual evaluations; there is one sub-evaluator for each construct listed under <b\_exp> in the grammar. The Eval function invokes the appropriate sub-evaluator depending on the type of the parse tree node ; the type of the tree node is determined by the value of the variant ( called Selector) - see figure 4-4. An overview of the way in which the evaluator works can be gained by the following examples:

<sup>&</sup>lt;sup>21</sup> See section 3.4.1 for clarification of these events.

There are two main categories of functions which are evaluated: higher-order functions (which take other BMF expressions as arguments and hence have children in their parse tree) and those which do not:

The following, simple, program:

B\_Op (B\_Plus) {2, 3}

when parsed produces the following single node parse tree:

When Eval is invoked, with this node and the input data, it will call the appropriate sub-evaluator which, in this case, is Eval\_B\_Op as identified by the node selector: B\_OP. Eval\_B\_Op then identifies the specific operation from the Operator field (in this case B\_Plus) and executes the appropriate operation on the program argument.

In contrast, the following example is a higher-order function, B\_Map:

B\_Map (\$INCREMENT) [1, 2, 3, 4]

which would produce the following parse tree:

Eval would invoke the sub-evaluator, Eval\_B\_Map, which would then perform the map operation in the following way:

For each item in input\_list Do

temp\_node := Eval(Pt\_Increment, item)

append temp\_node to result

End Do

where Pt\_Increment is the parse tree of \$Increment which is the child of the B\_Map node referenced by C1. The necessity of the Eval function being polymorphic is highlighted, in this example, because it allowed the Eval function to be called recursively with a different function (\$Increment).

## 4.6 Modelling of Parallel Execution

Simulated parallelism is facilitated in the evaluator by each data item being tagged with the Processor Id on which it resides and each virtual processor having its own clock stored in the *Machine Module*. When an operation is evaluated, the evaluator determines the location of the argument from its tag, and updates the corresponding virtual clock according to the length of the operation. To illustrate this, consider the following example:

P\_Map (\$Increment) [  $1^0$ ,  $2^1$ ,  $3^2$ ,  $4^3$  ]

The argument list is assumed to be distributed across four virtual processors as indicated by the superscripts. Evaluation proceeds in the same manner as with B\_Map(\$Increment), described previously, except that, in this case, each list item is assumed to reside on a different processor and hence, a separate processor clock is incremented with each invocation of Eval(\$Increment, Item). This reduces the simulated execution time by a factor of four when compared to the case when a single processor is involved.

#### 4.6.1 Tags

Lists are the only data structures capable of being spread across the machine and therefore each item within the list must have its own tag: the tag is referred to as 'Proc\_Id' in the record definition for the list\_node type as shown in Figure 4-2. Other types, including tuples, may not be spread across the machine and so only require a

single tag which identifies the processor on which they reside; tags for such data are also called 'Proc\_Id' which is a field in the Value record definition - see figure 4-2.

## 4.6.2 Machine Module

The state of the parallel machine is stored in a data structure called the 'Machine Module'. Presently, the machine module is effectively an array of clocks, indexed by processor id. Such a design allows extra attributes of each processor to be stored: for example a 'memory\_used' attribute could be added to facilitate the modeling of space consumption for each processor versus time. As can be seen from figure 4-1, both the evaluator and network modules access the machine module when they update the clocks.

With each invocation of the evaluator, an operation that consumes time proceeds in the following general manner:

- The current processor, P, is determined by inspecting the tag of the Item.

- The current time, T, is read from the appropriate virtual processor clock in the machine module.

- A Start\_Busy<sup>22</sup>(P, T) event is issued to signal the commencement of the computation.

- The specified operation is performed.

- The virtual processor clock is updated according to the length of the operation (T<sub>op</sub>).

- An End\_Busy(P,  $T+T_{op}$ ) event is issued to signal the end of computation.

#### 4.6.3 Inter-Process Communications

Parallelism, in BMF, involves two broad categories of operations: those such as P\_Map which act upon pre-distributed data and those which involve the transfer of data via inter-processor communications such as P\_Reduce and P\_Split. Within the evaluator, the location of data is changed by simply altering the tag, however to

<sup>&</sup>lt;sup>22</sup> Start\_Busy is equivalent to Stop\_Idle and Stop\_Busy is equivalent to Start\_Idle

simulate the effects of a real interconnection network, any inter-processor data movements are also associated with a call to the network module. These calls generate the appropriate trace information and also update the virtual clocks to take account of the communications delays.

# 4.7 Interconnection Network Modelling

There are two mechanisms by which the evaluator interacts with the network module: Normal and Delayed send.

## 4.7.1 Normal Send

For every inter-processor communication involved in executing the parallel operators, except P\_Project and P\_Scan, 'Normal Send' is invoked by the evaluator. Normal send has the following Ada specification:

The parameters are: Source - Source Processor